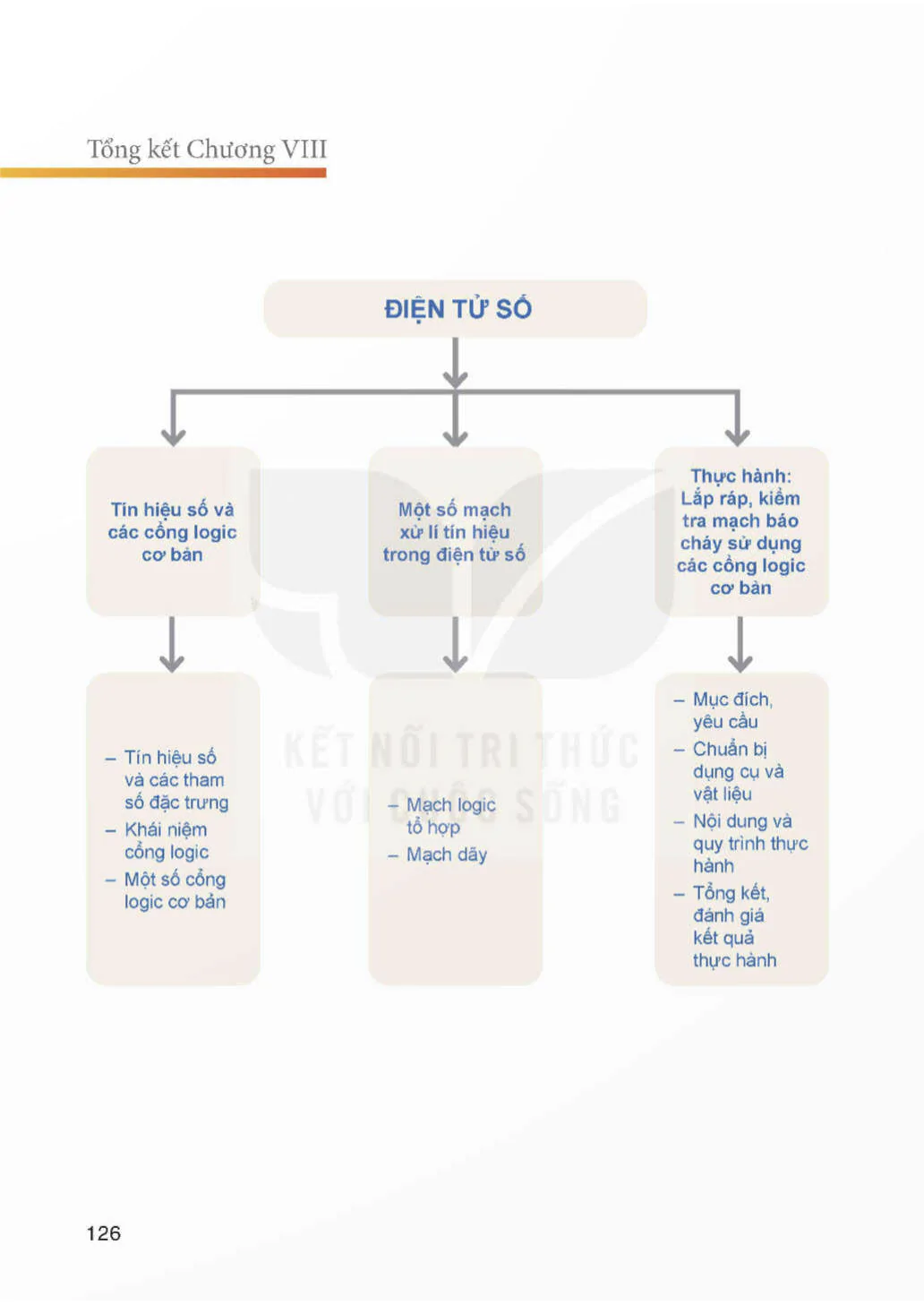

Nội Dung Chính

(Trang 118)

Sau khi học xong bài này, em sẽ:

Trình bày được một số mạch xử lí tín hiệu trong điện tử số.

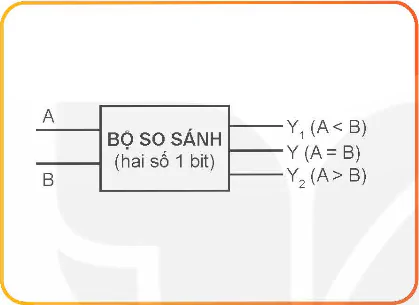

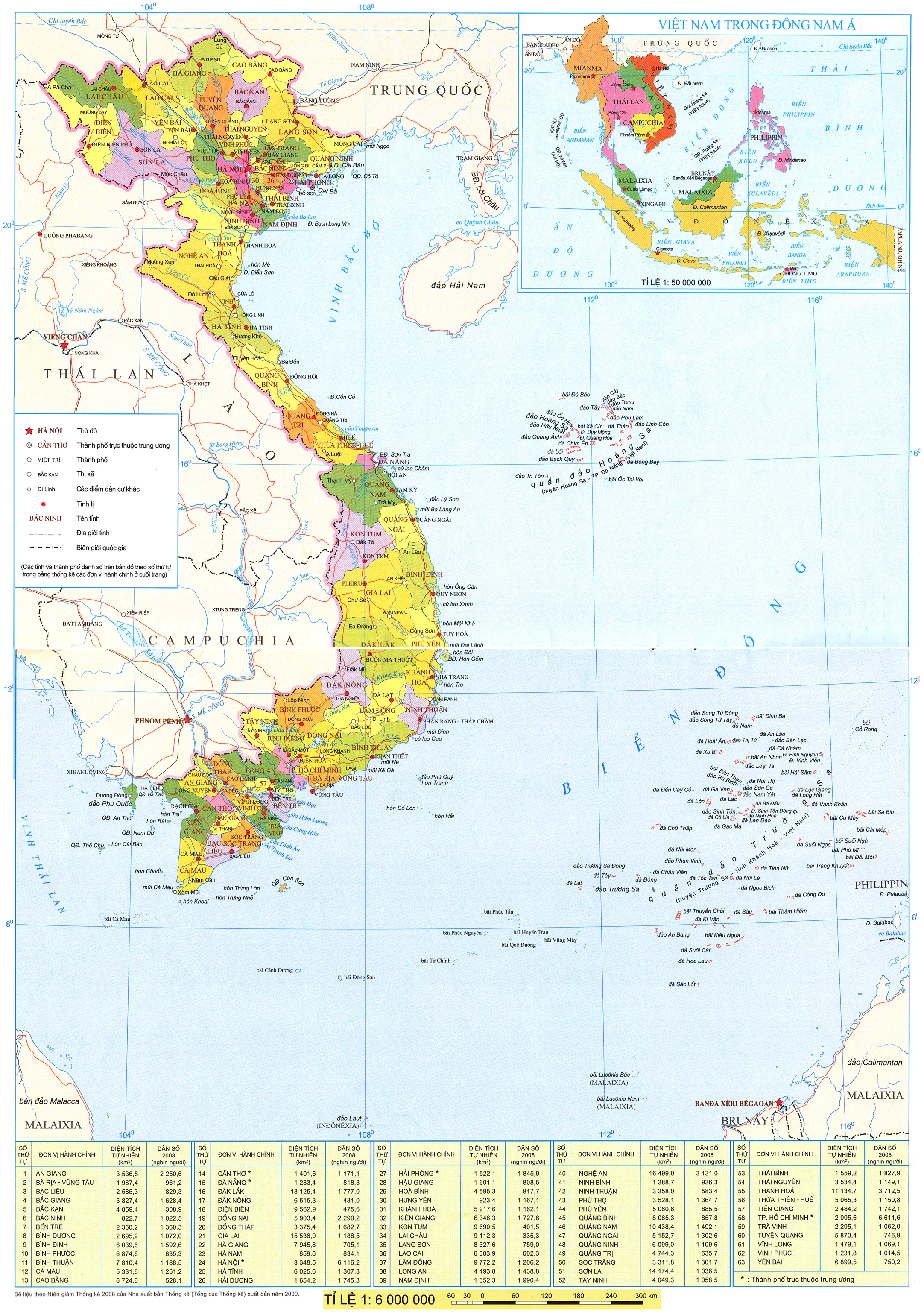

A; B; BỘ SO SÁNH (hai số 1 bit); Y1 (A < B); Y (A = B); Y2 (A > B)

Hình 22.1

Quan sát Hình 22.1 và cho biết khi so sánh hai số nhị phân A và B (1 bit) thì có những khả năng nào xảy ra?

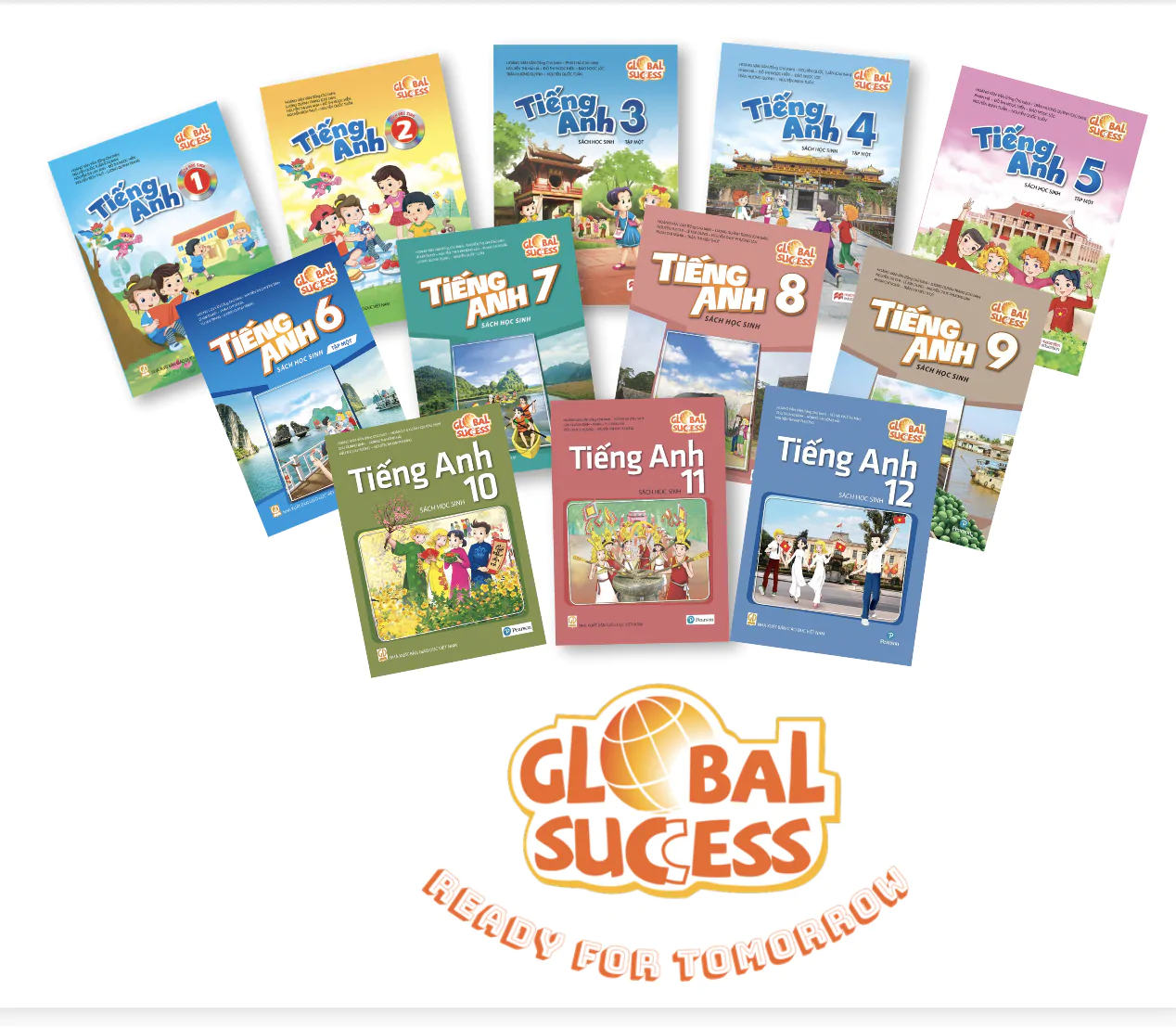

I. MẠCH LOGIC TỔ HỢP

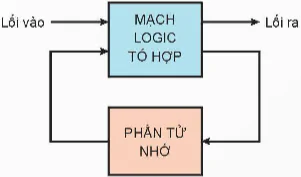

1. Khái niệm mạch logic tổ hợp

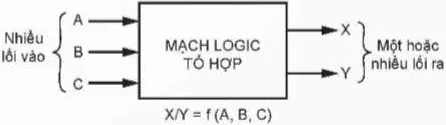

Mạch logic tổ hợp (Hình 22.2) là mạch được tạo thành từ các cổng logic cơ bản, trạng thái lối ra của mạch tại một thời điểm bất kì chỉ phụ thuộc vào tổ hợp các trạng thái logic ở lối vào tại thời điểm hiện tại mà không phụ thuộc vào trạng thái lối ra ở thời điểm trước đó (trạng thái quá khứ).

Các mạch logic tổ hợp bao gồm:

1) Các mạch số học (cộng, trừ,...).

2) Các bộ hợp kênh, phân kênh.

3) Các bộ mã hoá, giải mã.

4) Các mạch so sánh.

5) Các bộ khoá, điều khiển logic,...

Nhiều lối vào  MẠCH LOGIC TỔ HỢP (X/Y = f (A, B, C)

MẠCH LOGIC TỔ HỢP (X/Y = f (A, B, C)  Một hoặc nhiều lối ra

Một hoặc nhiều lối ra

Hình 22.2. Sơ đồ khối mạch logic tổ hợp

(Trang 119)

2. Mạch so sánh hai số

Mạch so sánh thực hiện chức năng so sánh hai số A và B (1 bit) trong đó:

- Nếu A = B thì lối ra C = 1.

- Nếu A # B thì lối ra C = 0.

Ta có bảng chân lí của mạch so sánh (Bảng 22.1).

Bảng 22.1. Bảng chân lí của mạch so sánh

| A | B | C | Kết luận |

| 0 | 0 | 1 | A = B |

| 0 | 1 | 0 | A # B |

| 1 | 0 | 0 | A # B |

| 1 | 1 | 1 | A = B |

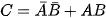

Từ bảng chân lí với các hàng C có giá trị bằng 1, ta viết được phương trình logic:  .

.

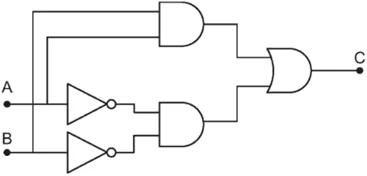

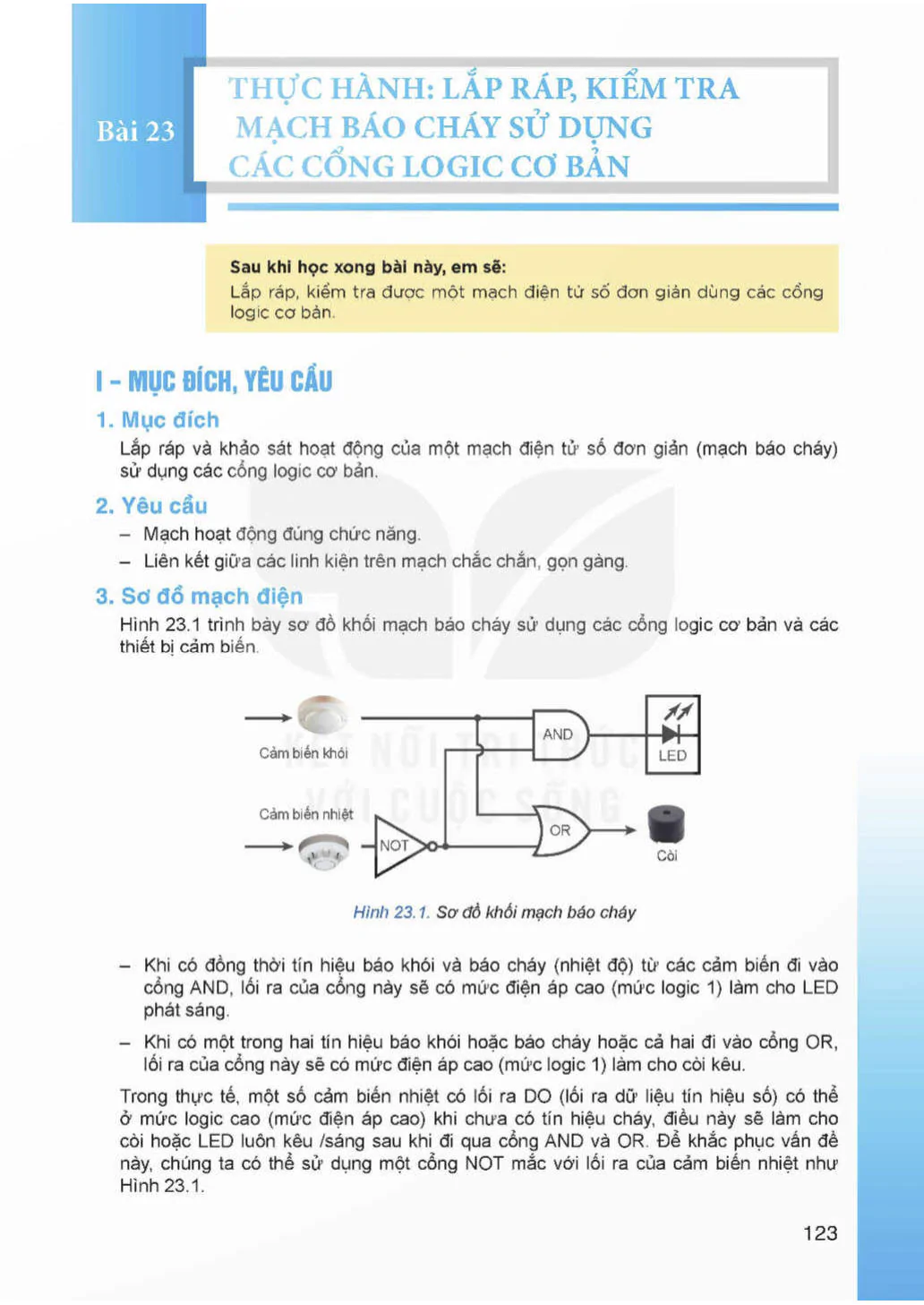

Từ phương trình logic ta thấy mạch sử dụng hai cổng NOT, hai cổng AND và một cổng OR. Sơ đồ logic của mạch được biểu diễn trong Hình 22.3.

Hình 22.3. Mạch so sánh hai số bằng nhau

II. MẠCH DÃY

1. Khái niệm mạch dãy

Mạch dãy (Hình 22.4) là mạch được tạo thành từ các cổng logic cơ bản, trạng thái lối ra của mạch không chỉ phụ thuộc vào tổ hợp các trạng thái lối vào ở thời điểm hiện tại mà còn phụ thuộc vào trạng thái logic ở lối ra của nó tại thời điểm trước đó (trạng thái quá khứ).

Các mạch dãy bao gồm:

1) Các phần tử nhớ.

2) Các Flip-Flop (Trigger).

3) Các bộ đếm.

4) Các bộ ghi dịch.

5) Các bộ chia tần.

Lối vào; MẠCH LOGIC TỔ HỢP; Lối ra; PHÂN TỬ NHỚ

Hình 22.4. Sơ đồ khối mạch dãy

(Trang 120)

2. Mạch đếm

Khám phá

Quan sát Hình 22.5, em hãy cho biết: Đèn tín hiệu giao thông thường thực hiện đếm tiến hay đếm lùi?

Hình 22.5. Đèn tín hiệu giao thông

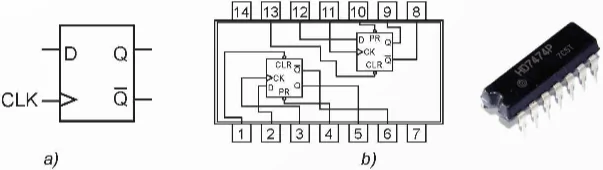

a) Flip-Flop (FF hay còn gọi là Trigger)

Flip-Flop là một phần tử nhớ có hai trạng thái cân bằng ổn định tương ứng với hai trạng thái logic 0 và 1. Dưới tác dụng của các tín hiệu điều khiển ở lối vào, FF có thể chuyển về một trong hai trạng thái cân bằng và giữ nguyên trạng thái đó chừng nào chưa có tín hiệu điều khiển tác động vào. Trạng thái tiếp theo của FF không chỉ phụ thuộc vào tin hiệu ở lối vào mà còn phụ thuộc vào cả trạng thái lối ra ở thời điểm hiện tại của nó.

Trên thực tế, có nhiều loại FF như RS, JS, T, D,... Tuy nhiên, trong bài học này chúng ta sẽ sử dụng Flip-Flop D (Hình 22.6) gồm:

- Lối vào dữ liệu D.

- Lối vào xung CLK.

- 2 lối ra Q và  (có trạng thái ngược nhau).

(có trạng thái ngược nhau).

Bảng 22.2. Bảng chân lí của Flip-Flop D

| CLK | D | Q |  | Trạng thái |

| ↓ | x | Q |  | Không thay đổi |

| ↑ | 0 | 0 | 1 | Xóa |

| ↑ | 1 | 1 | 0 | Đặt |

Ví dụ: Kí hiệu, sơ đồ chân và IC HD7474 tích hợp hai Flip-Flop D được cho trên Hình 22.6.

Hình 22.6. Kí hiệu, sơ đồ chân và IC tích hợp hai Flip-Flop D (HD7474)

(Trang 121)

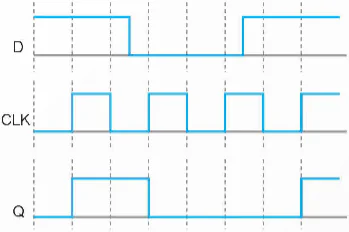

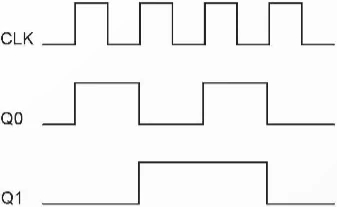

Hình 22.7 trình bày giản đồ thời gian của Flip-Flop D:

Hình 22.7. Giản đồ thời gian của Flip-Flop D

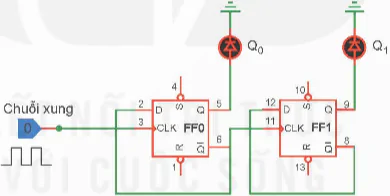

b) Mạch đếm nhị phân hai bit sử dụng Flip-Flop D

Mạch đếm nhị phân là thành phần cơ bản của hệ thống số, dùng để đếm số xung, chia tần số tạo xung thời gian làm các xung đồng hồ dùng trong máy tính và thiết bị thông tin.

Mạch đếm nhị phân trong Hình 22.8 là mạch đếm nhị phân nối tiếp (lối ra của FF trước đưa vào lối vào CLK của FF sau), thực hiện đếm tiến. Xung đồng hồ được đưa vào lối vào CLK của FF0 làm chuyển trạng thái của FF0, lối ra  của FF0 lại được đưa tới lối vào CLK của FF1 làm chuyển trạng thái của FF1.

của FF0 lại được đưa tới lối vào CLK của FF1 làm chuyển trạng thái của FF1.

Hình 22.8. Sơ đồ đếm nhị phân 2 bit

Từ sơ đồ ta có: FFO chuyển trạng thái (Q0 từ 0 lên 1 hoặc từ 1 về 0) với mọi xung nhịp tác dụng; FF1 chuyển trạng thái khi Q0 từ 1 về 0.

Ta có bảng chân lí của bộ đếm nhị phân 2 bit:

Bảng 22.3. Bảng chân lí của bộ đếm nhị phân 2 bit

| Xung vào | Q1 | Q0 | Giá trị thập phân |

| Xóa | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 2 | 1 | 0 | 2 |

| 3 | 1 | 1 | 3 |

(Trang 122)

Mạch thực hiện đếm từ 0 đến 3, khi xung thứ tư tác dụng, mạch trở lại trạng thái ban đầu, tiếp tục một chu trình đếm mới. Hình 22.9 trình bày giản đồ thời gian của bộ đếm.

Hình 22.9. Giản đồ thời gian của bộ đếm nhị phân 2 bit

Luyện tập

Xây dựng bộ đếm nhị phân ba bit sử dụng Flip-Flop D. Vẽ mạch, giải thích nguyên lí hoạt động, lập bảng chân lí và trình bày giản đồ thời gian của bộ đếm.

Vận dụng

Em hãy cho biết đồng hồ hiển thị trên cây xăng hoạt động dựa trên bộ so sánh, bộ đếm hay cả hai.

i+ Thông tin bổ sung

Phương pháp thiết kế các mạch logic tổ hợp

Với một mạch logic tổ hợp bất kì, nếu cho trước chức năng, ta đều có thể thiết kế và thực hiện được. Các bước tiến hành như sau:

1) Từ yêu cầu chức năng, ta lập bảng chân lí của hàm.

2) Từ bảng chân lí, ta suy ra phương trình/hàm logic.

3) Tối giản (rút gọn) hàm logic.

4) Từ hàm logic, vẽ mạch sử dụng các phần tử logic cơ bản.

Bình Luận

Để Lại Bình Luận Của Bạn